High-Efficiency High-Energy-Density Buffer Architecture for Power Pulsation Decoupling in Grid-Tied Applications

High-Efficiency High-Energy-Density Buffer Architecture for Power Pulsation Decoupling in Grid-Tied Applications

Shibin Qin with adviser R. Pilawa-Podgurski

Power conversion between dc and single-phase ac (inverters and rectifiers) requires an energy buffer for the twice-line-frequency power pulsation. This function is conventionally fulfilled with large electrolytic capacitors that suffer from poor efficiency and a short lifetime. In my project, a high-efficiency high-energy-density buffer architecture is proposed for this application. It is an active decoupling solution that allows for the use of film or ceramic capacitors for better reliability, while yielding improved efficiency and reduced circuit complexity, compared to state-of-art active decoupling solutions. By connecting a buffer converter in series with the main decoupling capacitor (schematic shown

in Fig. 3), the main capacitor is allowed larger ripple for improved energy utilization (and thus much reduced volume), while the dc bus voltage is maintained close to being ripple free. The buffer converter has low voltage stress and is processing only a fraction of the entire architecture’s total power, allowing a very small active circuit volume and high system efficiency. A control scheme is proposed to exploit the small remaining bus ripple to compensate the power loss in the power converter and balance the power cycle of the buffer architecture. All these technologies combined produce a highly efficient, compact energy buffer widely applicable to many grid-tied applications.

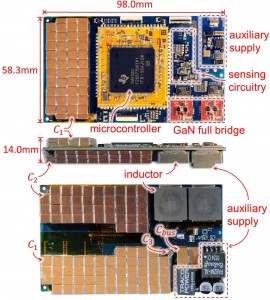

In this project, a 2kW hardware prototype has been built to demonstrate the benefit of the proposed solution, as shown in Fig. 4. The hardware prototype achieves a seven-times capacitance reduction and two-times overall volume reduction compared to the conventional passive decoupling solution.

Research for this design used in our entry to the Google/IEEE “Little Box” challenge was funded by Texas Instruments.