Differential Power Processing for Voltage Regulation of Series-Stacked Processor Cores to Improve Dynamic Performance

Dipanjan Das with adviser P. Krein

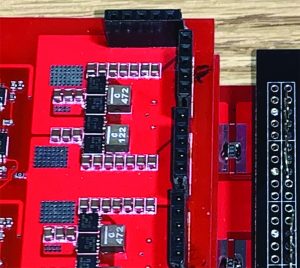

Figure 21: Bi-directional multi-phase buck/buck-boost converter with asymmetric current-sharing: hardward setup

Power delivery to multi-core processors is becoming increasingly challenging with decreasing transistor sizes and, thereby, their operating voltages. With the increase in the core number in each processor, the power requirements tend to remain the same with each new generation of microprocessors, and handling transient performance requirements along with efficiency has become much more difficult at lower voltages. Significant improvement in energy efficiency can be achieved by stacking the processor cores in series and regulating the core voltages by differential power processing (DPP). However, for practically achieving higher efficiency than the conventional parallel-connected processor cores, other (software) overheads are required to balance the power consumption of each processor core (such as communication between different voltage domains, scheduling processes to aid voltage balancing, etc.). Presently, control schemes for improvement in the dynamics and light load efficiency of the DPP voltage regulator are being developed.

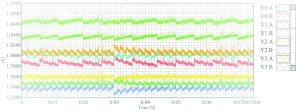

One particular topology suitable for voltage regulation of a series-stack of digital loads is the hierarchical element-to-element topology. It has been established that this topology provides improved dynamic performance compared to other non-isolated topologies in regulating stack voltages. Implementation of the bidirectional DPP converters has been one area of focus. A bi-directional multi-phase buck/buck-boost converter with asymmetric current sharing was developed for improved efficiency over a wide load range. Higher light-load efficiencies of individual DPP converters is expected to significantly improve system-level efficiencies. The present hardware setup (Figure 21) achieves a peak efficiency of over 90% over a load range of 100x (100mA to 10A) under different mismatch conditions, while maintaining 10% voltage regulation at 1.8V (Figure 22). This research is funded by the Grainger Center for Electric Machinery and Electromechanics.