Differential Power Processing for Voltage Regulation of Series-Stacked Processor Cores

Differential Power Processing for Voltage Regulation of Series-Stacked Processor Cores

MSEE student Dipanjan Das with adviser P. Krein

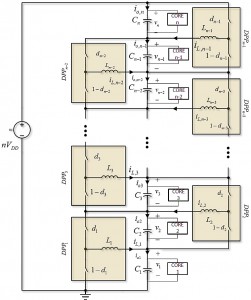

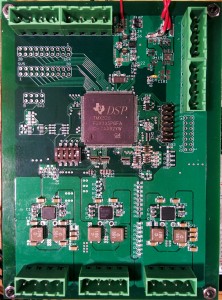

Power delivery to multi-core processors has become increasingly challenging as transistor sizes decrease and operating voltages thereby decrease. With the growing number of cores in each processor, power requirements tend to remain the same, but handling output impedance requirements of processors as supply voltages get lower and lower is difficult. Significant improvement in energy efficiency can be achieved by stacking the cores in series (thereby increasing the output voltage requirement and relaxing the output impedance requirement for the outer loop converter) and regulating the core voltages by differential power processing (DPP). The element-to-element DPP configuration (Fig. 1) seems to be most appropriate for our purpose because of its modularity and ease of integration. However for the conventional load-to-load architecture, which comprises back-to-back connected buck-boost converters, the dynamic response is demanding due to the coupled nature of the architecture. A large number of these converters cannot be connected back to back if the goal is fast transient response. Modified topologies derived from the load-to-load DPP topology are being analyzed. Developed hardware shown in Fig. 2 was tested to deliver 50W of power to a series stack of four voltage domains at 98% efficiency under 10% current mismatch between loads.

This research is supported by the Strategic Research Initiative, Engineering at Illinois.