Control and Design of Power Factor Correction System with Flying Capacitor Multilevel Boost Front-end and Active Energy Buffer

Zitao Liao with adviser R. Pilawa-Podgurski

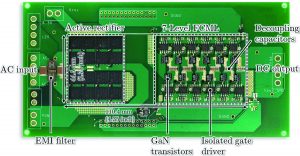

Power factor correction front-ends are widely used in ac-dc conversion applications. For conventional boost-converter based designs, two of the major limitations to achieve high power density are the size of the boost converter’s input filter inductor and the twice-line frequency energy buffer capacitor bank. In this work, the input-filter inductor size is reduced by leveraging the benefits of flying capacitor multilevel (FCML) topology. A 1.5 kW 7-level flying capacitor multilevel (FCML) hardware prototype is shown in Figure 23. The energy buffer at the output is implemented with series-stacked buffer (SSB) architecture that requires less capacitance than a passive capacitor bank. This work explores the unique control challenges of integrating FCML and SSB for PFC applications and identifies the potential of improvements on the overall system power density compared to conventional solutions. This research is supported by Texas Instruments.