Improving Microprocessor Power Delivery by Connecting Voltage Domains in Series

Pradeep Shenoy with advisor P.T. Krein

Microprocessors need power at low voltages (around 1 V) and high currents (100 A or more at full load). Supply voltages will be even lower as transistor sizes get smaller. Dynamically lowering the voltage of a digital circuit is beneficial in many applications because it reduces power consumption. However, this trend to lower voltage has a negative impact on conventional power delivery architectures. Additional down-conversion stages may be

necessary, increased bus capacitance is needed to meet voltage regulation specifications during load transients, and output impedance and efficiency requirements are harder to meet as the output voltage is lowered. Some

have proposed integrating voltage regulators on-chip but this creates many challenges of its own. Many in industry realize that a “nonlinear” breakthrough in power delivery

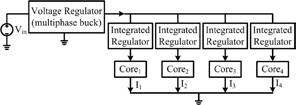

is needed. Present approaches are shown in Figure 32.

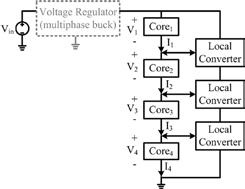

This research develops a new paradigm in power delivery that enables low supply voltages for digital circuits. Voltage domains are connected in series to enhance system efficiency and performance (shown in Figure 33). Multiple, independent voltage levels enabled by this approach can reduce power consumption dramatically by allowing each load element to operate in its region of highest efficiency. The power delivery circuits are also operated in an energy-optimal manner. Since voltage regulators process only a fraction of total load power at the intermediate nodes, improved performance, decreased size, decreased cost, and lower conversion losses are realizable. The number of cascaded step-down conversion stages can be reduced as the combined load voltage increases, even when individual circuits operate at supply levels far below 1 V.

Applying the new paradigm involves regulating each intermediate node (core). These regulation circuits are necessary to maintain the desired local load voltage in the presence of load-current mismatches. A mismatch occurs when the steady-state current demand for each series load is not identical. Some regulation can be accomplished by balancing the computational load among the load elements, but, in general, local voltage regulation circuits are still needed. This research proposes efficient switch-mode voltage regulation techniques that can be generalized to systems with a very large number of series components.